CMOS集成電路設(shè)計 原理、流程與關(guān)鍵技術(shù)

CMOS(互補金屬氧化物半導體)集成電路設(shè)計是現(xiàn)代電子工業(yè)的基石,廣泛應用于計算機、通信、消費電子等領(lǐng)域。隨著摩爾定律的持續(xù)演進,CMOS技術(shù)不斷推動集成電路向更高集成度、更低功耗和更高性能方向發(fā)展。本文將從CMOS集成電路的基本原理、設(shè)計流程和關(guān)鍵技術(shù)三個方面進行闡述。

一、CMOS集成電路的基本原理

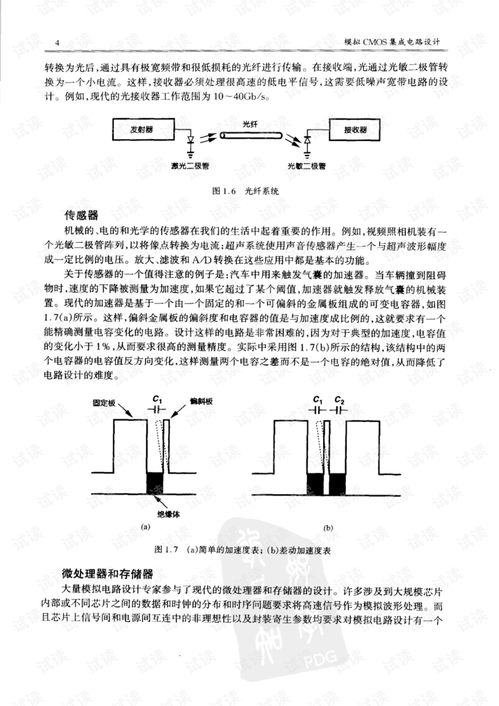

CMOS技術(shù)基于MOSFET(金屬氧化物半導體場效應晶體管)的互補特性,通過組合P型MOS和N型MOS晶體管實現(xiàn)邏輯功能。其核心優(yōu)勢在于靜態(tài)功耗極低,僅在實際開關(guān)操作時消耗能量。CMOS電路的基本結(jié)構(gòu)包括反相器、與非門、或非門等基本邏輯單元,這些單元通過特定連接方式構(gòu)成復雜的數(shù)字系統(tǒng)。CMOS技術(shù)還支持模擬電路設(shè)計,如運算放大器和數(shù)據(jù)轉(zhuǎn)換器,實現(xiàn)了數(shù)模混合信號集成。

二、CMOS集成電路設(shè)計流程

CMOS集成電路設(shè)計遵循一套系統(tǒng)的流程,通常包括以下階段:

- 規(guī)格定義:明確電路的功能、性能、功耗和成本要求。

- 架構(gòu)設(shè)計:確定系統(tǒng)整體結(jié)構(gòu),如數(shù)據(jù)路徑、控制邏輯和存儲器配置。

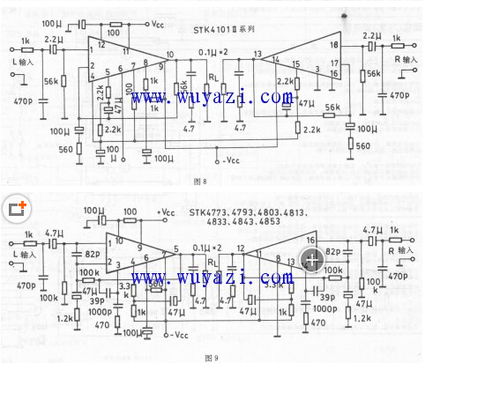

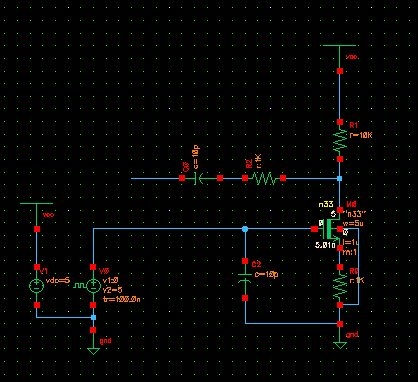

- 電路設(shè)計:使用SPICE等工具進行晶體管級仿真,優(yōu)化電路性能。

- 版圖設(shè)計:將電路轉(zhuǎn)換為物理布局,考慮器件匹配、寄生效應和制造規(guī)則。

- 驗證與仿真:通過DRC(設(shè)計規(guī)則檢查)、LVS(版圖與原理圖一致性檢查)和后仿真確保設(shè)計正確性。

- 流片與測試:將設(shè)計提交給晶圓廠制造,并進行硅片測試驗證。

三、CMOS設(shè)計的關(guān)鍵技術(shù)

- 低功耗設(shè)計:采用多閾值電壓、電源門控和動態(tài)電壓頻率縮放等技術(shù)降低功耗。

- 納米尺度挑戰(zhàn):隨著工藝節(jié)點進入納米級,短溝道效應、量子隧穿和互連延遲成為主要問題。

- 設(shè)計自動化:EDA(電子設(shè)計自動化)工具如Cadence和Synopsys支持從RTL到GDSII的全程設(shè)計。

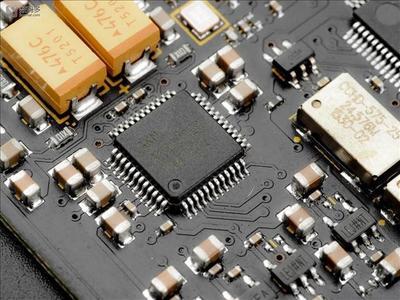

- 異構(gòu)集成:通過3D-IC和SiP(系統(tǒng)級封裝)技術(shù)整合不同工藝的芯片,提升系統(tǒng)性能。

未來,CMOS集成電路設(shè)計將繼續(xù)向更小節(jié)點、更高能效和智能化方向發(fā)展,結(jié)合新材料(如二維半導體)和新架構(gòu)(如神經(jīng)形態(tài)計算),為下一代電子產(chǎn)品賦能。

如若轉(zhuǎn)載,請注明出處:http://www.yvqxth.cn/product/16.html

更新時間:2026-04-06 13:32:50