印制電路板EMC設(shè)計技巧與集成電路設(shè)計的融合

電磁兼容性(EMC)設(shè)計在現(xiàn)代電子系統(tǒng)中至關(guān)重要,尤其對于印制電路板(PCB)和集成電路(IC)設(shè)計。有效的EMC設(shè)計可以減少電磁干擾(EMI),確保設(shè)備穩(wěn)定運行,并滿足相關(guān)法規(guī)標(biāo)準(zhǔn)。以下是一些關(guān)鍵的設(shè)計技巧,結(jié)合了PCB和集成電路層面的策略。

一、印制電路板EMC設(shè)計技巧

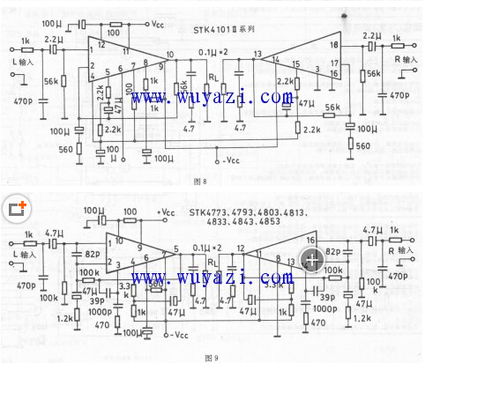

- 分層與布局優(yōu)化:采用多層PCB板,將電源層和接地層緊密相鄰,以形成低阻抗回路。信號層應(yīng)位于電源層和接地層之間,以減少輻射。關(guān)鍵高速信號線應(yīng)布放在內(nèi)層,避免表層走線。

- 接地策略:實施單點或多點接地,根據(jù)頻率選擇。高頻電路宜用多點接地,低頻電路可用單點接地。確保接地平面完整,避免分割,以減少地回路噪聲。

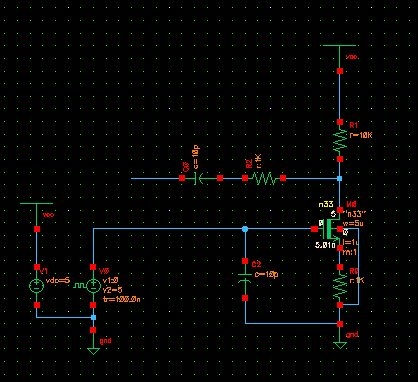

- 去耦與濾波:在電源引腳附近放置去耦電容(如0.1μF和10μF),以抑制高頻噪聲。對于敏感信號,添加EMI濾波器,如RC或LC電路,以衰減干擾。

- 信號完整性管理:控制信號線的阻抗匹配,使用差分對傳輸高速信號,減少共模噪聲。避免長走線和銳角轉(zhuǎn)彎,采用45度或弧形布線,以最小化反射和輻射。

- 屏蔽與隔離:對高頻或噪聲敏感區(qū)域使用屏蔽罩,或?qū)⒚舾薪M件物理隔離。在PCB上設(shè)置隔離帶,防止數(shù)字和模擬電路之間的耦合。

二、集成電路設(shè)計中的EMC考慮

- 芯片級EMC設(shè)計:在IC設(shè)計階段,集成片上濾波器和去耦電容,以降低對外部元件的依賴。采用低噪聲放大器(LNA)和鎖相環(huán)(PLL)設(shè)計,優(yōu)化電源管理單元(PMU)以減少開關(guān)噪聲。

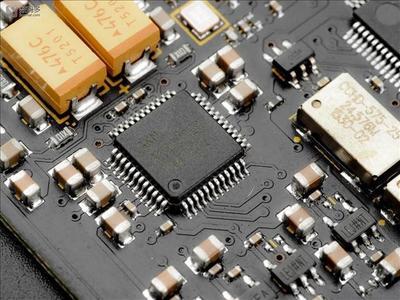

- 封裝與引腳分配:選擇適當(dāng)?shù)腎C封裝(如BGA或QFN),以提供良好的接地和電源引腳。合理分配引腳,將噪聲源與敏感引腳隔離,例如將時鐘引腳遠離模擬輸入。

- 片上隔離技術(shù):使用Guard rings或深阱隔離工藝,在芯片內(nèi)隔離噪聲模塊,防止 substrate 耦合。對于混合信號IC,實施數(shù)字和模擬域的物理分離。

- 仿真與測試:在IC設(shè)計流程中,進行EMC仿真(如使用SPICE或?qū)I(yè)工具),預(yù)測電磁行為。結(jié)合后硅測試,驗證EMC性能,并根據(jù)結(jié)果迭代優(yōu)化。

三、系統(tǒng)級集成策略

將PCB和IC設(shè)計結(jié)合,實現(xiàn)整體EMC優(yōu)化。例如,在PCB布局時考慮IC的EMC特性,避免將噪聲IC放置在敏感區(qū)域。同時,利用IC的內(nèi)部功能(如時鐘展頻)來降低系統(tǒng)級EMI。通過跨層級協(xié)作,從芯片到板級,確保電磁兼容性。

EMC設(shè)計是一個系統(tǒng)工程,需要從PCB布局到集成電路內(nèi)部結(jié)構(gòu)的全面考慮。通過應(yīng)用這些技巧,可以顯著提升電子產(chǎn)品的可靠性和合規(guī)性,減少開發(fā)后期的整改成本。實踐表明,早期集成EMC設(shè)計能帶來更高的效率和性能。

如若轉(zhuǎn)載,請注明出處:http://www.yvqxth.cn/product/13.html

更新時間:2026-04-06 05:29:01