集成電路版圖設(shè)計基礎(chǔ)知識

集成電路是現(xiàn)代電子設(shè)備的核心,而版圖設(shè)計則是集成電路設(shè)計過程中至關(guān)重要的一步。它決定了電路的物理結(jié)構(gòu)、性能以及制造成本。本文將介紹集成電路版圖設(shè)計的基本概念、流程和關(guān)鍵原則。

一、什么是集成電路版圖

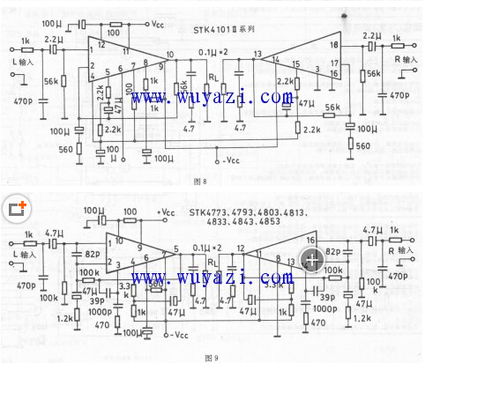

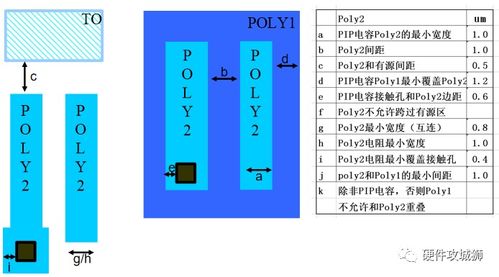

集成電路版圖(Layout)是指將電路設(shè)計轉(zhuǎn)換為物理圖形的過程。這些圖形包括晶體管、電阻、電容等元件的幾何形狀和位置,以及它們之間的連接線路。版圖設(shè)計需要遵循制造工藝的規(guī)則,以確保芯片能夠正確制造并達(dá)到預(yù)期的電性能。

二、版圖設(shè)計的基本流程

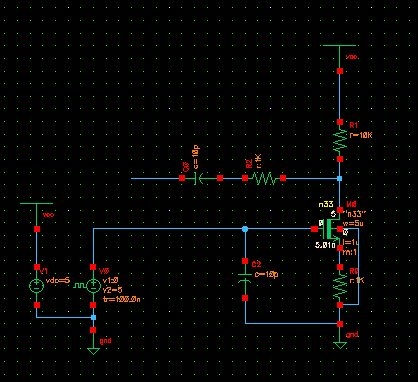

- 電路設(shè)計:設(shè)計人員根據(jù)功能需求設(shè)計電路圖(如使用Verilog或VHDL進(jìn)行邏輯設(shè)計)。

- 版圖規(guī)劃:確定芯片的整體布局,包括功能模塊的位置和電源規(guī)劃。

- 元件放置:將晶體管和其他元件放置在芯片上,考慮性能、功耗和面積優(yōu)化。

- 布線:連接各個元件,確保信號和電源路徑的完整性。

- 驗證:通過設(shè)計規(guī)則檢查(DRC)、電氣規(guī)則檢查(ERC)和版圖與電路圖對比(LVS)等步驟,確保版圖符合制造要求和設(shè)計意圖。

- 輸出:生成用于制造的GDSII文件。

三、版圖設(shè)計的關(guān)鍵原則

- 設(shè)計規(guī)則:必須嚴(yán)格遵守制造工藝的設(shè)計規(guī)則,包括最小線寬、間距和層次對齊等,以避免制造缺陷。

- 性能優(yōu)化:通過版圖布局減少寄生電容和電阻,提高電路速度和功耗效率。

- 面積最小化:合理布局以減小芯片面積,從而降低成本。

- 可靠性考慮:避免熱點、電遷移等問題,確保芯片長期穩(wěn)定運行。

四、常用工具和工藝

版圖設(shè)計通常使用專業(yè)工具,如Cadence Virtuoso、Synopsys IC Compiler等。這些工具支持自動布局和布線,但設(shè)計人員仍需手動優(yōu)化關(guān)鍵部分。工藝方面,常見的包括CMOS工藝,其版圖涉及多圖層(如多晶硅、金屬層和接觸孔)。

五、總結(jié)

集成電路版圖設(shè)計是連接電路設(shè)計和實際制造的橋梁。掌握版圖基礎(chǔ)知識,包括流程、規(guī)則和優(yōu)化技巧,對于設(shè)計高性能、低成本的芯片至關(guān)重要。隨著工藝節(jié)點不斷縮小(如7nm、5nm),版圖設(shè)計變得更加復(fù)雜,要求設(shè)計人員具備更高的專業(yè)知識和經(jīng)驗。

如若轉(zhuǎn)載,請注明出處:http://www.yvqxth.cn/product/12.html

更新時間:2026-04-06 18:23:52